Semiconductor Parametric Test System

![]()

Overview of Equipment

Support from the package level to the wafer level

As wafers become larger in diameter, smaller in size, and more highly integrated, reliability testing of single unit transistors is becoming increasingly important.

This system can measure the electrical characteristics and continuous changes of high accuracy voltage and current application and FET single unit transistors, collect the data on a computer, monitor the data, and perform other central management tasks.

Main specifications

Please scroll horizontally to look at table below.

| Model | AMM-C (Package Level) | AMM-W (Wafer Level) |

|---|---|---|

| Measurement program | FET single unit transistor measurement library, 48 types | |

| Temperature control | Temperature chamber (ESPEC bench-top type temperature (& humidity) chamber SU-662) | Full, semi-auto, manual prober (Contact us about the manufacturer) |

| Temperature control range -60 to +150°C | ||

| SMU performance | Voltage ±50 V / current ±100 mA | |

| DUT connection | DUT board (6 sockets) ・DIP600mil, 28pins ・DIP300mil, 16pins Selection |

Positioner Probe card(for high temperature, micro current) * Available depending on the layout. |

Features

- Batch processing of multiple DUTs

- Simultaneously applies stress to and measures up to 108 SMUs on the package level and up to 324 SMUs on the wafer level.

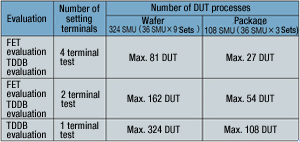

- Number of DUT processes

- * Additional software (optional) is required to perform TDDB evaluation.

- Highly-accurate application and measurement of voltage and current

- The accuracy of the multi SMU has a range of 2 voltages and 9 currents at ±50 V/±100 mA, and the system can apply and measure a wide range with a resolution of 1 mV/1 pA.

- FET single unit transistor characteristics support TDDB evaluation

- Using the 2-terminal (Drain/Gate) and 4-terminal (Drain/Gate/Base/Source) settings, the FET single unit transistor can evaluate I-V characteristics, HCI, and NBTI.

In addition, the optional TDDB evaluation software can be used to evaluate TDDB, TZDB, SBD, QDB, I-V, BDV, and more.

- Use software to change pin assignments

- Change the terminal settings by cabinet (36 SMUs ×3 sets). In addition, changes can be made to the pad layout for the same number of terminals on the application for each multi SMU, thereby enabling changes to the pin assignments with the same probe guard.

- Avoid electrostatic breakdown

- To avoid static electricity from human bodies, a short connector is provided that prevents damage to the FET. The wiring on the DUT board is guarded to the socket source so as not to be affected by electrical noise. (Package level evaluation)

- DUT board with short connector (test area)

Recommended products for customers viewing this product

- Contact us

- Customer Support Desk

Measurement & Evaluation Systems / Semiconductor-related Equipment

-

Measurement & Evaluation Systems

- Electro-chemical Migration Evaluation System(Leakage Current Evaluation System)

- High Voltage Bias Insulation Resistance Evaluation System

- Capacitor Leakage Test System

- High Temperature Reverse Bias Test System

- TDDB (Time-Dependent Dielectric Breakdown) Evaluation System

- Conductor Resistance Evaluation System

- Electromigration Evaluation System

- PV Thermal-Bias Combo Test System

- Semiconductor Parametric Test System

- Capacitor / Inductor Temperature Characteristic Evaluation System

- PV I-V Evaluation System (PV Thermal-Light Combo Test System)

- Power Cycle Test System

- Semiconductor-related Equipment