Power cycling test system

For joint reliability evaluation of

power semiconductors

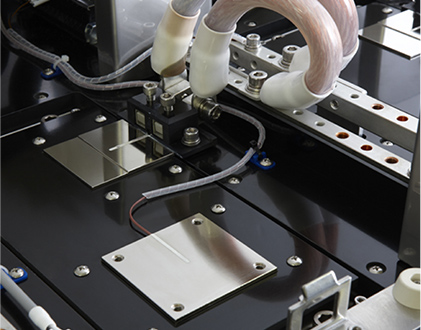

ESPEC offer chambers for joint reliability evaluation of power semiconductors used in a wide variety of fields, including automotive, home appliances, mobile devices, and industrial machinery.

The system applies a large current to the power semiconductor and heats the device chips to raise their temperature to the target high temperature, then interrupts the current, dropping them to the target low temperature to apply temperature stress. This process is repeated to subject the device to heat stress. The heat causes stress fractures, and the reliability of the wire bonding with the chip is evaluated.

Test category

- Power cycling test(long power cycling, short power cycling)

Test devices

- MOSFET

- IGBT

- IPM

etc.

Keywords

- Power cycling test system

- Power semiconductor

- Large current

- Wire bonding

POINT 01Specifications tailored to the sample

ESPEC can provide the optimal equipment configurations to match your devices to be tested, including stress power supplies, switch units, gate drive circuits, etc.

You can choose from air- or water-cooling depending on the heat generation of your device.

We offer time-fixed control or temperature target control (Tvj or Tc) depending on the testing method.

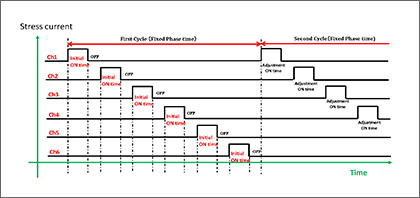

POINT 02ESPEC proprietary testing algorithms deliver streamlined testing

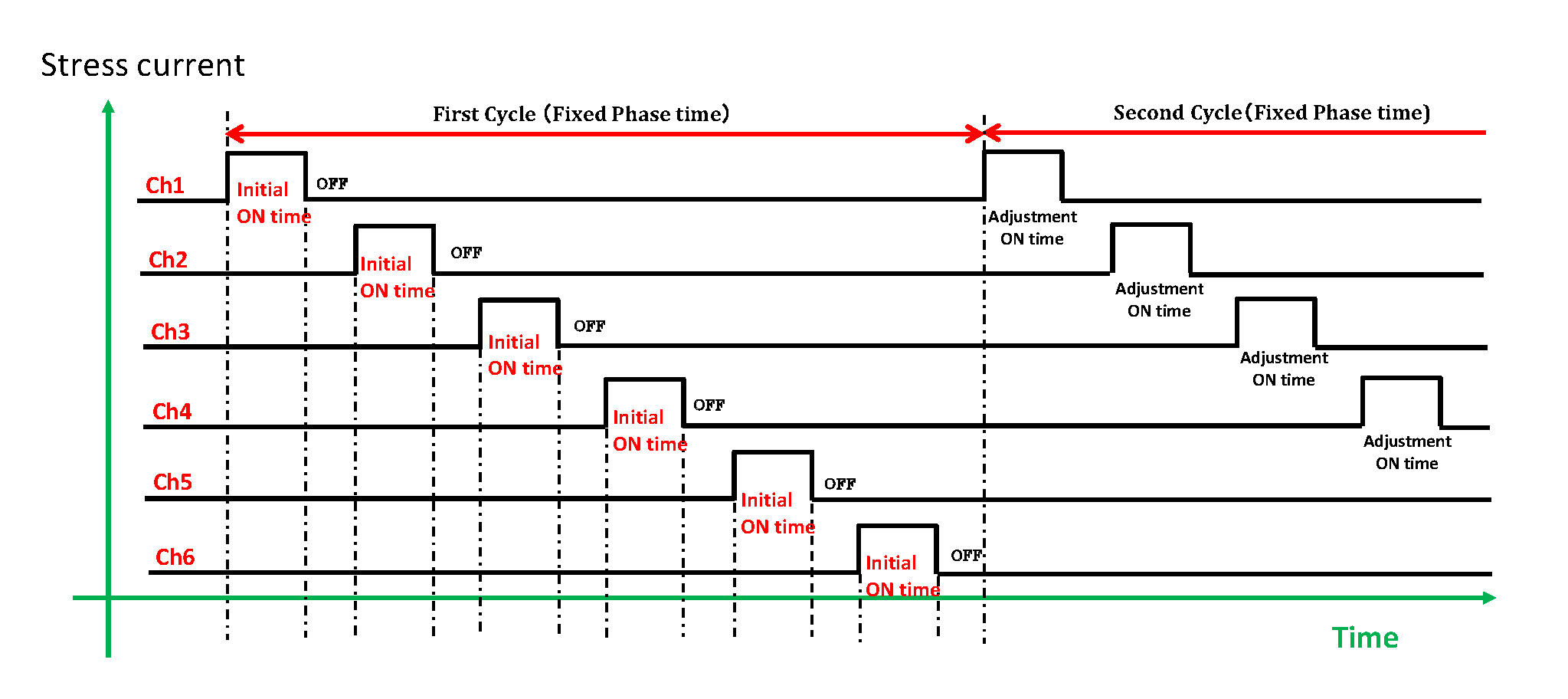

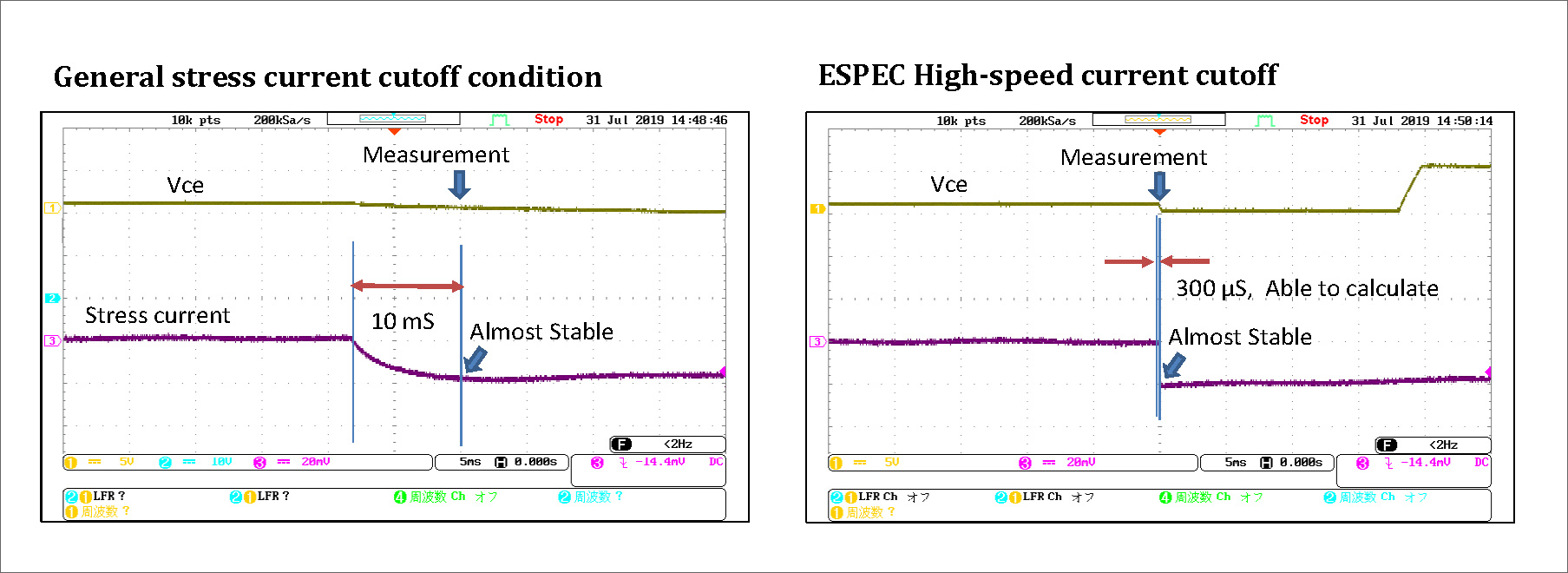

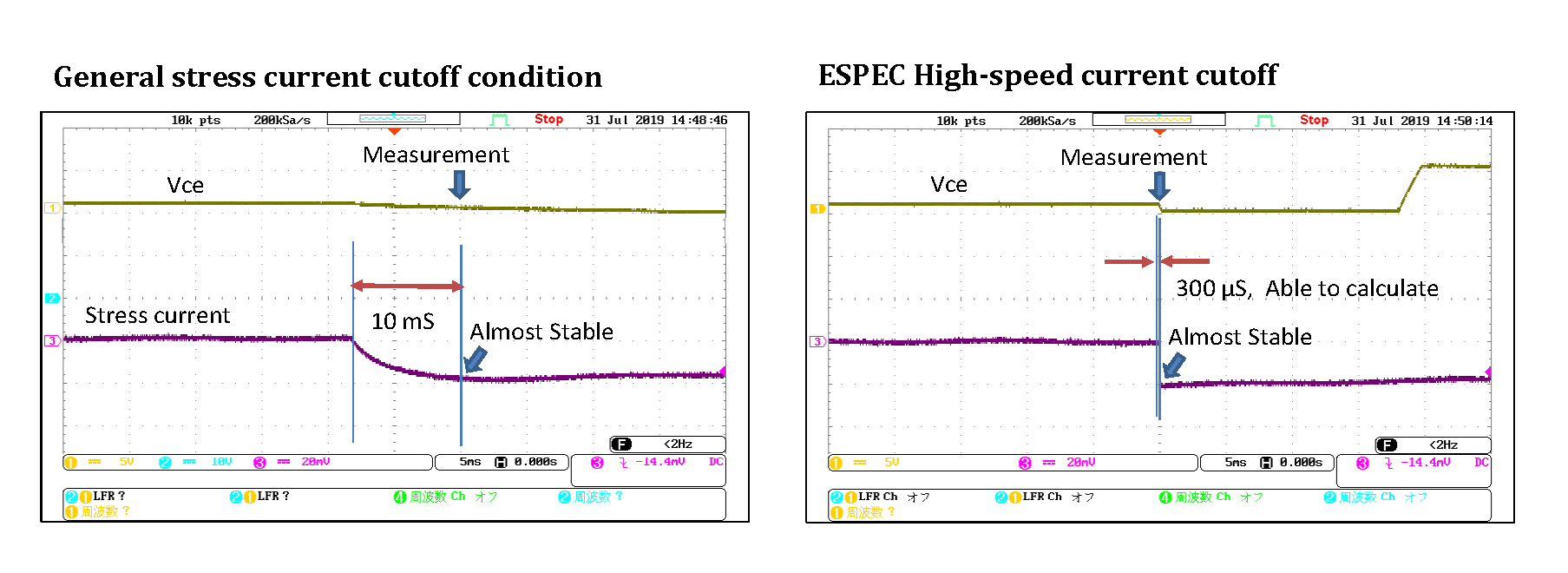

POINT 03Our proprietary constant current unit provides high-speed stress current ON/OFF control

With this chamber, you can select from two application methods depending on the test conditions: constant current mode and constant power mode.

In constant current mode, the system is equipped with a proprietary constant current unit that can suppress overshoot during current application.

This quickly interrupts the stress current, delivering Tvj measurement 300μs after the current is turned off.

POINT 04Excess thermal resistance measurement function *under development

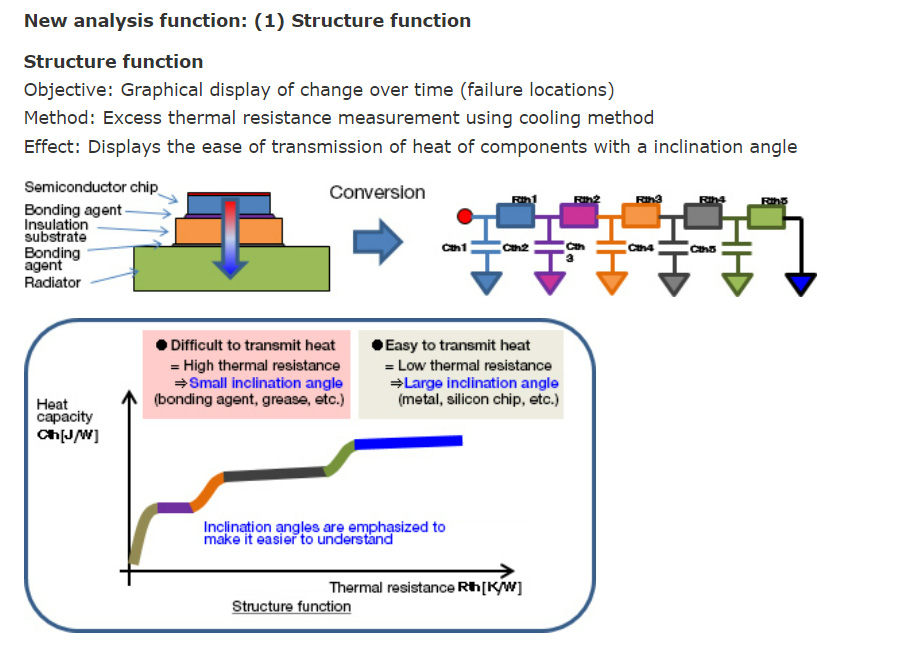

The structure function allows for evaluation of the thermal characteristics of each structure.

The graph that shows the time and semiconductor chip temperature increase characteristics is converted to create a characteristic graph that expresses via tilt how heat is conducted in each material along a single heat channel from the heat source to the radiator. ESPEC are currently making preparations for release.

Specifications

| Measurement system | |||

|---|---|---|---|

| Measurement mode | Base model | Option | |

| Characteristic measurement | TCR measurement | ○ | |

| Temperature transient response measurement | ○ | ||

| Test mode | Time fixed control | ○ | |

| Tj temperature control | ○ | ||

| Tc temperature control | ○ | ||

| Vf control | ○ | ||

| Superimpose | ○ | ||

| Continuously energized | ○ | ||

| Application mode | Constant current mode | ○ | |

| Constant power mode | ○ | ||

| Time fixed, Tj target | ○ | ||

| Analysis mode | Heat capacity/heat insulation (structure function) |

○ | |

| Tj/cycle(sequential data) | ○ | ||